व्हॉटअॅप/वेचॅट: 008618589033832

स्काईप: संनिष्ठुआनबीएसपी

मध्ये शक्ती अखंडता सुरक्षित करण्यासाठी तीन पैलूपीसीबी डिझाइनिंग

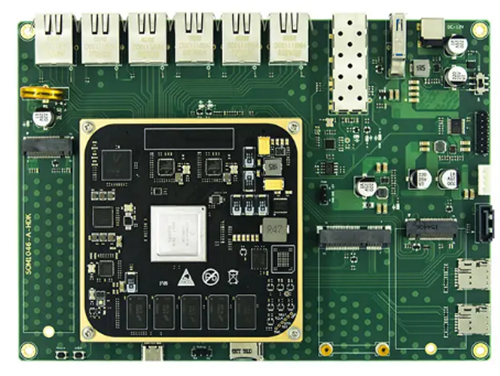

आधुनिक इलेक्ट्रॉनिक डिझाइनमध्ये, पॉवर अखंडता पीसीबी डिझाइनचा एक अपरिहार्य भाग आहे. इलेक्ट्रॉनिक उपकरणांचे स्थिर ऑपरेशन आणि कार्यप्रदर्शन सुनिश्चित करण्यासाठी, आम्ही उर्जा स्त्रोतापासून प्राप्तकर्त्यापर्यंत विस्तृतपणे विचार करणे आणि डिझाइन करणे आवश्यक आहे.

पॉवर मॉड्यूल्स, अंतर्गत थर विमाने आणि वीज पुरवठा चिप्स काळजीपूर्वक डिझाइन आणि ऑप्टिमाइझद्वारे आम्ही खरोखर उर्जा अखंडता प्राप्त करू शकतो. हा लेख पीसीबी डिझाइनर्ससाठी व्यावहारिक मार्गदर्शन आणि रणनीती प्रदान करण्यासाठी या तीन प्रमुख बाबींचा शोध घेईल.

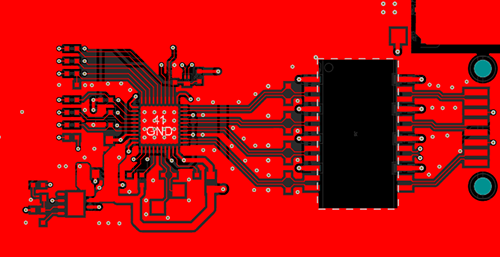

I. पॉवर मॉड्यूल लेआउट वायरिंग

पॉवर मॉड्यूल प्रत्येक इलेक्ट्रॉनिक उपकरणांचा उर्जा स्त्रोत आहे, त्याची कार्यक्षमता आणि लेआउट संपूर्ण सिस्टमच्या स्थिरता आणि कार्यक्षमतेवर थेट परिणाम करते. योग्य लेआउट आणि राउटिंग केवळ आवाजातील हस्तक्षेप कमी करू शकत नाही तर गुळगुळीत चालू प्रवाह देखील सुनिश्चित करू शकते, ज्यामुळे एकूण कामगिरी सुधारेल.

2. पॉवर मॉड्यूल लेआउट

1. स्त्रोत प्रक्रिया:

पॉवर मॉड्यूलला विशेष लक्ष दिले पाहिजे कारण ते शक्तीचा प्रारंभिक बिंदू म्हणून काम करते. आवाजाचा परिचय कमी करण्यासाठी, इतरांना जवळपास टाळण्यासाठी पॉवर मॉड्यूलच्या सभोवतालचे वातावरण शक्य तितके स्वच्छ ठेवले पाहिजेउच्च-वारंवारताकिंवा आवाज-संवेदनशील घटक.

२. वीजपुरवठा चिपवर बंद करा:

पॉवर मॉड्यूल शक्य तितक्या पॉवर-पुरवठा केलेल्या चिपच्या जवळ ठेवावे. यामुळे सध्याच्या ट्रान्समिशन प्रक्रियेतील तोटा कमी होऊ शकतो आणि अंतर्गत थर विमानाच्या क्षेत्राची आवश्यकता कमी होऊ शकते.

He. उष्णता नष्ट करण्याच्या विचारात:

ऑपरेशन दरम्यान पॉवर मॉड्यूल उष्णता निर्माण करू शकते, म्हणून हे सुनिश्चित केले पाहिजे की उष्णता नष्ट होण्याकरिता त्यापेक्षा जास्त अडथळे नाहीत. आवश्यक असल्यास, शीतकरणासाठी हीटसिंक्स किंवा चाहते जोडले जाऊ शकतात.

4. ओव्हॉईडिंग लूप्स:

रूटिंग करताना, इलेक्ट्रोमॅग्नेटिक हस्तक्षेपाची शक्यता कमी करण्यासाठी वर्तमान लूप तयार करणे टाळा.

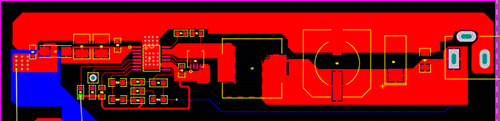

Ii. अंतर्गत स्तर विमान डिझाइन नियोजन

ए लेयर स्टॅक डिझाइन

In पीसीबी ईएमसी डिझाइन, लेयर स्टॅक डिझाइन हा एक मुख्य घटक आहे ज्यास मार्ग आणि उर्जा वितरणाचा विचार करणे आवश्यक आहे.

अ. पॉवर प्लेनची कमी प्रतिबाधा वैशिष्ट्ये सुनिश्चित करण्यासाठी आणि ग्राउंड नॉईज कपलिंग शोषून घेण्यासाठी, शक्ती आणि ग्राउंड प्लेनमधील अंतर 10 मिलपेक्षा जास्त नसावे, सामान्यत: 5 मिलपेक्षा कमी असण्याची शिफारस केली जाते.

बी. जर एकच उर्जा विमान लागू केले जाऊ शकत नाही, तर उर्जा विमान घालण्यासाठी पृष्ठभागाचा थर वापरला जाऊ शकतो. जवळपास जवळची शक्ती आणि ग्राउंड प्लेन कमीतकमी एसी प्रतिबाधा आणि उत्कृष्ट उच्च-वारंवारता वैशिष्ट्यांसह विमान कॅपेसिटर तयार करतात.

सी. आवाज जोडण्यापासून रोखण्यासाठी जवळपास दोन पॉवर थर, विशेषत: मोठ्या व्होल्टेज फरकांसह टाळा. अपरिहार्य असल्यास, शक्य तितक्या दोन पॉवर थरांमधील अंतर वाढवा.

डी. संदर्भ विमाने, विशेषत: पॉवर संदर्भ विमाने, कमी प्रतिबाधा वैशिष्ट्ये राखली पाहिजेत आणि बायपास कॅपेसिटर आणि लेयर ments डजस्टमेंटद्वारे ऑप्टिमाइझ केले जाऊ शकतात.

बी. मल्टिपल पॉवर सेगमेंटेशन

अ. विशिष्ट आयसी चिपच्या कोर वर्किंग व्होल्टेजसारख्या विशिष्ट लहान-श्रेणी उर्जा स्त्रोतांसाठी, पॉवर प्लेनची अखंडता सुनिश्चित करण्यासाठी तांबे सिग्नल लेयरवर ठेवला पाहिजे, परंतु ध्वनी विकिरण कमी करण्यासाठी पृष्ठभागाच्या थरावर उर्जा तांबे घालणे टाळा.

बी. विभाजन रुंदीची निवड योग्य असावी. जेव्हा व्होल्टेज 12 व्हीपेक्षा जास्त असेल तेव्हा रुंदी 20-30 मिल असू शकते; अन्यथा, 12-20 मिल निवडा. एनालॉग आणि डिजिटल उर्जा स्त्रोतांमधील विभाजन रुंदी एनालॉग पॉवरमध्ये हस्तक्षेप करण्यापासून प्रतिबंधित करण्यासाठी वाढविणे आवश्यक आहे.

सी. रूटिंग लेयरवर साधे उर्जा नेटवर्क पूर्ण केले जावे आणि लांब पॉवर नेटवर्कमध्ये फिल्टर कॅपेसिटर जोडले पाहिजेत.

डी. अनियमित आकार टाळण्यासाठी सेगमेंट्ड पॉवर प्लेन नियमित ठेवले पाहिजे ज्यामुळे अनुनाद आणि वाढीव शक्ती प्रतिबाधा वाढेल. लांब आणि अरुंद पट्ट्या आणि डंबबेल-आकाराच्या विभागांना परवानगी नाही.

सी. प्लेन फिल्टरिंग

अ. पॉवर प्लेन ग्राउंड प्लेनसह जवळून जोडले जावे.

बी. 500 मेगाहर्ट्झपेक्षा जास्त ऑपरेटिंग फ्रिक्वेन्सी असलेल्या चिप्ससाठी, प्रामुख्याने प्लेन कॅपेसिटर फिल्टरिंगवर अवलंबून असतात आणि कॅपेसिटर फिल्टरिंगचे संयोजन वापरा. पॉवर इंटिग्रिटी सिम्युलेशनद्वारे फिल्टरिंग इफेक्टची पुष्टी करणे आवश्यक आहे.

सी. पॉवर ग्राउंड प्रतिबाधा लक्ष्य प्रतिबाधापेक्षा कमी आहे हे सुनिश्चित करण्यासाठी कंट्रोल प्लेनवर डिकॉपलिंग कॅपेसिटर, जसे की कॅपेसिटर लीड्स वाढविणे आणि कॅपेसिटर व्हियास वाढविण्यासाठी इंडक्टर्स स्थापित करा.

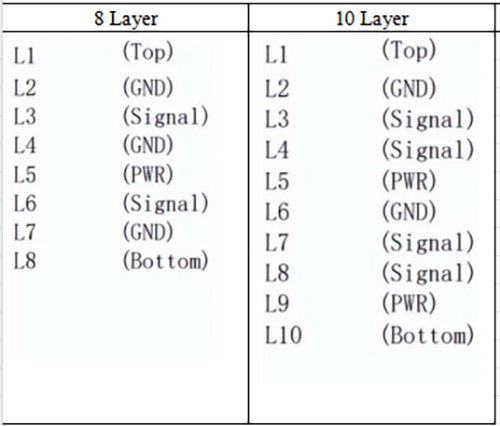

Iii. पॉवर चिप लेआउट वायरिंग

पॉवर चिप इलेक्ट्रॉनिक उपकरणांचे मूळ आहे आणि डिव्हाइसची कार्यक्षमता आणि स्थिरता सुधारण्यासाठी त्याची शक्ती अखंडता सुनिश्चित करणे महत्त्वपूर्ण आहे. पॉवर चिप्ससाठी पॉवर इंटिग्रिटी कंट्रोलमध्ये प्रामुख्याने चिप पॉवर पिन हाताळणी आणि योग्य लेआउट आणि डिकॉपलिंग कॅपेसिटरचे वायरिंग समाविष्ट असते. खाली या पैलूंशी संबंधित विचार आणि व्यावहारिक सल्ला तपशीलवार दिल्या जातील.

ए. चिप पॉवर पिन राउटिंग

चिप पॉवर पिनचे मार्ग पॉवर अखंडता नियंत्रणाचा एक महत्त्वपूर्ण भाग आहे. स्थिर सद्य पुरवठा प्रदान करण्यासाठी, पॉवर पिनचे मार्ग दाट करण्याची शिफारस केली जाते, सामान्यत: चिप पिन सारख्याच रूंदीवर. थोडक्यात, दकिमान रुंदी8 मिलपेक्षा कमी असू नये, परंतु चांगल्या परिणामासाठी, 10 मिलची रुंदी मिळविण्याचा प्रयत्न करा. राउटिंगची रुंदी वाढवून, प्रतिबाधा कमी होऊ शकते, ज्यामुळे उर्जा आवाज कमी होईल आणि चिपला पुरेसा सद्य पुरवठा सुनिश्चित होईल.

बी. लायआउट आणि डिकॉपलिंग कॅपेसिटरचे मार्ग

पॉवर चिप्ससाठी पॉवर इंटिग्रिटी कंट्रोलमध्ये डिकॉपलिंग कॅपेसिटर महत्त्वपूर्ण भूमिका बजावतात. कॅपेसिटर वैशिष्ट्ये आणि अनुप्रयोगांच्या आवश्यकतांवर अवलंबून, डिकॉपलिंग कॅपेसिटर सामान्यत: मोठ्या आणि लहान कॅपेसिटरमध्ये विभागले जातात.

अ. मोठे कॅपेसिटर: मोठे कॅपेसिटर सहसा चिपच्या सभोवताल समान रीतीने वितरित केले जातात. त्यांच्या कमी अनुनाद वारंवारता आणि मोठ्या फिल्टरिंग त्रिज्यामुळे, ते कमी-वारंवारता आवाज प्रभावीपणे फिल्टर करू शकतात आणि स्थिर वीजपुरवठा करू शकतात.

बी. लहान कॅपेसिटर: लहान कॅपेसिटरमध्ये रेझोनंट वारंवारता आणि लहान फिल्टरिंग त्रिज्या असतात, म्हणून त्यांना चिप पिनच्या शक्य तितक्या जवळ ठेवावे. त्यांना खूप दूर ठेवणे प्रभावीपणे उच्च-फ्रिक्वेन्सी आवाज फिल्टर करू शकत नाही, ज्यामुळे डिक्प्लिंग प्रभाव गमावला. योग्य लेआउट हे सुनिश्चित करते की उच्च-वारंवारता आवाज फिल्टरिंगमध्ये लहान कॅपेसिटरच्या प्रभावीतेचा पूर्णपणे उपयोग केला जातो.

C. समांतर डिकॉपलिंग कॅपेसिटरची वायरिंग पद्धत

उर्जा अखंडता सुधारण्यासाठी, एकाधिक डिकॉपलिंग कॅपेसिटर बर्याचदा समांतर जोडलेले असतात. या अभ्यासाचा मुख्य हेतू समांतर कनेक्शनद्वारे वैयक्तिक कॅपेसिटरची समकक्ष मालिका इंडक्टन्स (ईएसएल) कमी करणे आहे.

एकाधिक डिकॉपलिंग कॅपेसिटर समांतर करताना, कॅपेसिटरसाठी व्हीआयएच्या प्लेसमेंटकडे लक्ष दिले पाहिजे. एक सामान्य प्रथा म्हणजे शक्ती आणि ग्राउंडची व्हियास ऑफसेट करणे. याचा मुख्य उद्देश डिकॉपलिंग कॅपेसिटरमधील परस्पर इंडक्टन्स कमी करणे आहे. म्युच्युअल इंडक्शनन्स एकाच कॅपेसिटरच्या ईएसएलपेक्षा खूपच लहान आहे याची खात्री करा, जेणेकरून एकाधिक डिकॉपलिंग कॅपेसिटर समांतरानंतर एकूण ईएसएल प्रतिबाधा 1/एन असेल. म्युच्युअल इंडक्टन्स कमी करून, सुधारित उर्जा स्थिरता सुनिश्चित करून, फिल्टरिंग कार्यक्षमता प्रभावीपणे वर्धित केली जाऊ शकते.

लेआउटआणि पॉवर मॉड्यूलचे मार्ग, अंतर्गत स्तर विमान डिझाइन नियोजन आणि पॉवर चिप लेआउट आणि वायरिंगची योग्य हाताळणी इलेक्ट्रॉनिक डिव्हाइस डिझाइनमध्ये अपरिहार्य आहे. योग्य लेआउट आणि रूटिंगद्वारे, आम्ही पॉवर मॉड्यूलची स्थिरता आणि कार्यक्षमता सुनिश्चित करू शकतो, आवाजाचा हस्तक्षेप कमी करू शकतो आणि एकूण कामगिरी सुधारू शकतो. लेयर स्टॅक डिझाइन आणि एकाधिक पॉवर सेगमेंटेशन पॉवर प्लेनची वैशिष्ट्ये अधिक अनुकूलित करते, उर्जा आवाजातील हस्तक्षेप कमी करते. पॉवर चिप लेआउट आणि वायरिंग आणि डिकॉपलिंग कॅपेसिटरची योग्य हाताळणी उर्जा अखंडता नियंत्रणासाठी महत्त्वपूर्ण आहे, स्थिर वर्तमान पुरवठा आणि प्रभावी ध्वनी फिल्टरिंग, डिव्हाइसची कार्यक्षमता आणि स्थिरता वाढविणे.

व्यावहारिक कामकाजात, सध्याची परिमाण, मार्ग रुंदी, व्हायसची संख्या, जोडप्याचे प्रभाव इत्यादी विविध घटकांचा तर्कसंगत लेआउट आणि मार्ग निर्णय घेण्यासाठी सर्वसमावेशक विचार करणे आवश्यक आहे. शक्ती अखंडतेचे नियंत्रण आणि ऑप्टिमायझेशन सुनिश्चित करण्यासाठी डिझाइन वैशिष्ट्ये आणि सर्वोत्तम पद्धतींचे अनुसरण करा. केवळ अशाप्रकारे आम्ही इलेक्ट्रॉनिक उपकरणांसाठी स्थिर आणि कार्यक्षम वीजपुरवठा प्रदान करू शकतो, वाढत्या कामगिरीच्या मागण्या पूर्ण करू शकतो आणि इलेक्ट्रॉनिक तंत्रज्ञानाचा विकास आणि प्रगती चालवू शकतो.

शेन्झेन अँके पीसीबी कंपनी, लिमिटेड

पोस्ट वेळ: मार्च -25-2024